该32位内核名为MIPS34K,采用90纳米工艺,频率为500MHz,实际上是更早的MSPS24的扩展产品,它带有DSP扩展功能,采用了MIPS公司所谓的对称多线程技术。该内核整合了多个硬件虚拟处理单元(VPE)和一个用于实时确定性操作的可选QoS逻辑块。

根据MIPS34K产品行销经理Vivek Sardana的介绍,对于需要DSP 和 RISC混合操作以及使用多操作系统的嵌入式消费类应用,上述整合可以获得比MIPS24K高达两倍的性能改善。

MIPS34K 产品的工程总监Darren Jones说,该内核在内部测试中,通过几个并行的EEMPC 基准测试后,其速度证明比早期的625MHz内核快60%。这种速度的增加是在仅使用了两个线程的条件下实现的,而且对高速缓存的影响很小。而其所占硅片的面积仅为72平方毫米裸片的14%。

Berkeley Design Technology Inc.(BDTI)公司的DSP分析师Kenton Williston表示,这种MIPS设计减小了几乎所有微处理器设计所遭遇的设计瓶颈效应,即:存储器延时、流水线延迟及其它因素引起的线程丢失而造成相关的流水线存在固有的低效性。

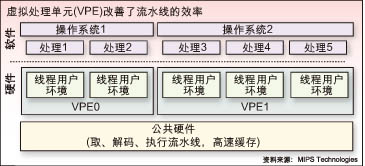

图:MIPS34K内核使用了“对称多线程”技术。

“对于绝大多数的微处理器结构而言,一个无法改变的事实是,对于每一个时钟周期,指令不能正常地发出。”RTOS vendor ExpressLogic市场副总裁John Carbone指出,“实际情况是,由于加载缓冲行或者CPU正在修复缓冲失败而导致指令周期中执行没有可用数据的无效操作,从而浪费了大量的时间。”

为了取回丢失的指令周期,并使因此增加的硅片面积小,MIPS多线程架构在硬件中保留了多用户环境(context),这样,在一个周期丢失时,处理器可以切换到另一个环境,并平衡利用好处理器流水线中的空隙。

MIPS34K内核采用了两个虚拟处理单元(VPE0 和VPE1),包括总共5个线程关联(TC)模块。Jones将VPE描述为MIPS32架构操作系统可视状态的一个实例,而将 TC描述为MIPS32的用户状态应用编程模型在硬件上的复制。“对于应用和操作系统而言,每一个VPE 或 TC就像一个全功能的CPU,允许我们同时使用多个操作系统、多个处理和多线程,”Jones说。并且因为VPE共享一个缓存,多线程设计具有固有的缓存一致性。

“MIPS34K的主要优点在于,如果不考虑可能发生的缓冲丢失所带来的成本,它提供了可以把任务间的切换成本降到零的硬件。”BDTI公司的 Williston评论道。

VPE/TC 结构似乎也能够减少缓冲丢失情况。“通常,几乎对于任何的微处理器设计来说,足有一半的周期会丢失,从而导致流水线的效率低下,或引起较长的存储器存取时延。”Carbone 说,“如果MIPS VPE/TC结构能够捕捉到这些被浪费的周期的足够的一部分,就能够在不需要额外的内核、流水线和更高的时钟速率情况下,将处理器的性能提高一倍,并且功耗要比其它方案降低很多。

不过,对于多媒体和网络功能密集的应用来说,Williston 不认为 MIPS34K是恰当的方案。“在某些场合,所获得的性能提高抵不上所带来的额外复杂度,而在另一些场合,却又得不到足够的性能改善。关键的问题是在于采用多线程虚拟处理单元架构的容易程度。”他说。

在有关该方案的扩展性,Express Logic 的 Carbone心存疑问:在实质上不增加内核裸片面积情况下,TC 和 VPE的数量能否增加?该方案能否为集成多个MIPS34K 内核设计带来好处?